Intel路線圖曝光:10nm產(chǎn)品在2018年底推出

來源:內(nèi)容來自快科技,謝謝。

在1月25日下午的財報會議上,Intel CEO Brian Krzanich(科再奇)對外明確表示,將在2018年晚些時候推出完全不受Meltdown和Spectre漏洞影響的芯片產(chǎn)品。

雖然在報告期內(nèi)(2017年Q4)Intel給出了創(chuàng)記錄的財務(wù)數(shù)據(jù),但華爾街分析師也提出了安全漏洞對未來Intel影響的擔(dān)心。

對此,科再奇表示,即便是把影響放大到最高,也不會對Intel未來的財務(wù)預(yù)期造成明顯干擾。他還補(bǔ)充說,Intel已經(jīng)安排了最強(qiáng)大腦來處理此事(指安全漏洞事件)。

同時,關(guān)于所謂的安全CPU產(chǎn)品究竟對應(yīng)誰,知名媒體PCworld和TMHW也給出了自己的分析。

PW稱,這款CPU產(chǎn)品應(yīng)該是基于14nm工藝的Cascade Lake-X或者部分10nm Cannon Lake芯片。Cascade Lake-X是下一代Core X發(fā)燒級處理器的代號,用以接替在售的Skylake-X,按照早先路線圖,定于Q4推出,時間倒是挺對的上號。

目前的Core X和普通酷睿的一個區(qū)別是,前者采用了Mesh bus網(wǎng)格互聯(lián)架構(gòu),而后者是Ring Bus環(huán)形總線。

至于這批新處理器是否會刺激Intel的銷量,PW認(rèn)為要分兩個領(lǐng)域看,消費(fèi)級不會,但企業(yè)級用戶可能會爭相選擇部署。

另一家權(quán)威硬件媒體TMHW和PW的看法基本一致,也就是10nm和新14nm都會有著底層級別的漏洞免疫。

關(guān)于先進(jìn)制程,科再奇在財報會議上表示,14nm的產(chǎn)品在2018年會繼續(xù)做下去。至于10nm,2017年末和2018上半年選擇小規(guī)模出貨,2018年下半年進(jìn)入大規(guī)模制造。

最后,PW和TMHW均提到,未來的Intel芯片可能會漲價。

雖然從理論上說,Intel在2017年夏天就已經(jīng)獲悉相關(guān)漏洞,所以后來的路線圖應(yīng)該就是修正過的,但前AMD專家現(xiàn)在Moor Insights首席分析師Pat Moorhead卻有著自己的看法,他稱Intel要么就是在為發(fā)布的芯片中直接集成了修復(fù),要不然就只能把新品延期1年。

英特爾:10nm的CPU性能提升25%,功耗下降45%

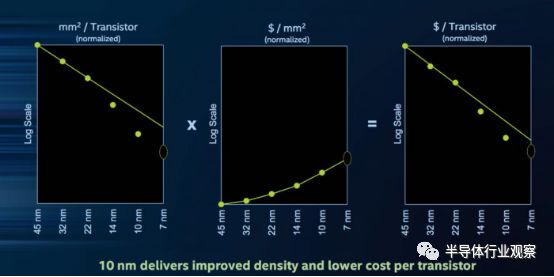

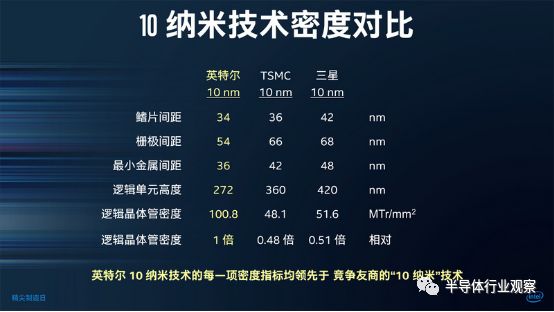

在去年舉辦的Technology and Manufacturing Day的活動上,英特爾表示,10nm能在1平方毫米的面積內(nèi)容納超過1億個晶體管,鰭片間距更小,10nm會和14nm一樣,會使用在三代產(chǎn)品上,而并不是之前的Tick-Tock模式,分別是10nm、10nm+、10nm++,在這之后才會進(jìn)入7nm,年底的10nm產(chǎn)品比起現(xiàn)在的14nm++,其在性能上能提升25%,功耗還降低45%,他們認(rèn)為英特爾的10nm工藝會比三星和臺積電的要更強(qiáng)。

英特爾高級院士Mark Bohr毫不保守的表示,通過采用超微縮技術(shù)(hyper scaling),英特爾10納米制程工藝擁有世界上最密集的晶體管和最小的金屬間距,從而實(shí)現(xiàn)了業(yè)內(nèi)最高的晶體管密度,領(lǐng)先其他競爭對手的10nm整整一代。

未來會怎樣發(fā)展?

到了 10 nm之后,我們不能像在以往節(jié)點(diǎn)一樣,通過簡單地縮小柵極寬度來推進(jìn)制程。7 nm勢必霈要昂貴的全新晶體管架構(gòu)、溝道材料和內(nèi)部連接。同時還需要全新的Fab 工具和材料。但就我們觀察,這些目前都不夠成熟。從技術(shù)的角度看來,我們可以生產(chǎn)7 mn或5 nm芯 片。但設(shè)計(jì)和生產(chǎn)這些制程的芯片,需要極強(qiáng)的資金 和能力。另外,在有多種選擇的當(dāng)下,如何選擇正確的 技術(shù)也是實(shí)現(xiàn)這些制程的關(guān)鍵。

從之前的路線來看,在7 nm制程,最有希望的晶體管候選者就是高電子遷移率的III-V族FinFET,而5nm,我們會迎來下一代全新的晶體管。(而根據(jù)IMEC的報告,下一代晶體管出現(xiàn)的時間是7nm,比我們預(yù)想的更早)

在7 nm的時候,有三種晶體管可以選擇,分別是環(huán)繞柵極場效應(yīng)晶體管、量子阱FinFET和SOI FinFET。 根據(jù)IMEC的報告,環(huán)繞柵極場效應(yīng)晶體管是最好的選擇。但是同樣,鍺或Ⅲ-V族材料都應(yīng)該是7 nm時溝道的首選材料。

關(guān)于7 nm時候的溝道材料的選擇,IMEC將其范圍縮窄到兩個:一個是由80%鍺組成的PFET;一種是 25%到50%混合鍺的FET和0到25%混合鍺且?guī)в?strain relaxed buffers的NFET。最完美的選擇材料是鍺。 硅器件的運(yùn)行電壓是0.8 v和0.75 v,而鍺器件的 工作電壓是0.5 v。毫無疑問,使用鍺讓我們降低了 Vdd,進(jìn)而降低了功耗。 而在7 nm之后,業(yè)界也給出了幾種晶體管選擇, 如上面提到的環(huán)形柵極、量子阱、SOl FinFET,還有 Ⅲ-V族FinFET和垂直納米線。IMEC表示他們正在考量垂直納米線的方方面面。同時他們也在探索如何生長溝道。

2017-01-29 來源:半導(dǎo)體行業(yè)觀察